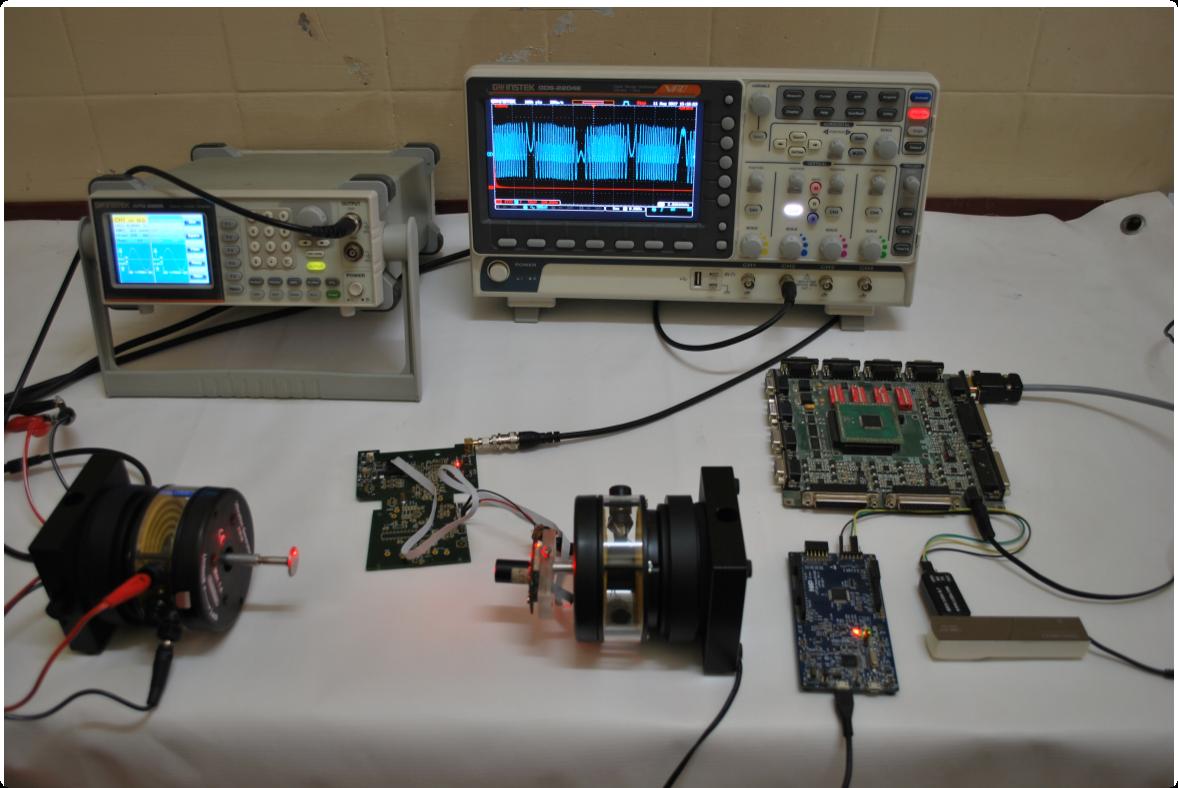

Teams of Digital System Design, Sensoing and Signal Processing from Riphah Int’l University, NUST, UCERD Pvt Ltd Islamabad and University de Toulouse France, developed A high performance real-time Interferometry Sensor System Architecture (ISSA).

Dr. Tassadaq Hussain is the team lead of this project. The work has been published in IEEE conference [1] [2] [3] and ScienceDirect Journal [4].

Dr. Tassadaq Hussain is the team lead of this project. The work has been published in IEEE conference [1] [2] [3] and ScienceDirect Journal [4].

Teams of Riphah Int’l University, NUST, UCERD and University de Toulouse France, Developed A high performance real-time Interferometry Sensor System Architecture

UCERD Rawalpindi

Supercomputing Center

UCERD Murree

ISSA is an easy to program, low-power and high-performance Interferometry Sensor System Architecture.

It takes complex high-speed data from interferometry sensors interface or saved in the memory, handles it in an on-chip memory system and processes them using dedicated hardware ac-

celerators or multi-RISC (Reduced Instruction Set Computer) processor system. The ISSA provides single-board hardware and software solution for sensor applications, by accessing high-speed data using Front-end Sensor Interface, placing it to local memory and processing it using heterogeneous multi-core processing system.

To hide the hardware complexity the ISSA provides sensor applications programming toolkit which provides data transfer, memory management, and processing function calls.

In order to valdate the ISSA three diverse sensor algorithms (CSU, IPUM, and TFSP) are targeted. CSU algorithm is the least precise algorithm among the three algorithms. However, due to the simplest processing, CSU is most efficient in terms of resources, speed, and power

consumption.

IPUM is a most precise algorithm, but more precision is achieved at cost of more resources, power and time utilization.

TFSP is in-between CSU and IPUM in terms of precision, resource utilization, time and power consumption. Salient contributions of the proposed ISSA are:

• Enables hardware/software co-design and parallel processing approach, by supporting multiple general purpose RISC and application specific hardware accelerator cores.

• Gives high-performance and real-time application support by using a memory system which manages computer intensive and time critical data and their complex transfers.

• Provides hardware reconfigurability by using application specific accelerators which allow sensor system architect to port more features in hardware without changing the system architecture.

• Consumes low power by utilizing a front-end interface that handles multiple sensors and their 1D/2D data transfers.

• Provides energy efficacy and high speed by using an on-chip scheduler which handles multiple sensors and processing cores.

• Offers programming toolkit which helps sensor application programmers to write their code easily and efficiently.

• When compared to a baseline sensor system, the ISSA improves the application performance up to 7.5 times, draws 15.6% less dynamic power and consumes 8.9 times less energy.

It takes complex high-speed data from interferometry sensors interface or saved in the memory, handles it in an on-chip memory system and processes them using dedicated hardware ac-

celerators or multi-RISC (Reduced Instruction Set Computer) processor system. The ISSA provides single-board hardware and software solution for sensor applications, by accessing high-speed data using Front-end Sensor Interface, placing it to local memory and processing it using heterogeneous multi-core processing system.

To hide the hardware complexity the ISSA provides sensor applications programming toolkit which provides data transfer, memory management, and processing function calls.

In order to valdate the ISSA three diverse sensor algorithms (CSU, IPUM, and TFSP) are targeted. CSU algorithm is the least precise algorithm among the three algorithms. However, due to the simplest processing, CSU is most efficient in terms of resources, speed, and power

consumption.

IPUM is a most precise algorithm, but more precision is achieved at cost of more resources, power and time utilization.

TFSP is in-between CSU and IPUM in terms of precision, resource utilization, time and power consumption. Salient contributions of the proposed ISSA are:

• Enables hardware/software co-design and parallel processing approach, by supporting multiple general purpose RISC and application specific hardware accelerator cores.

• Gives high-performance and real-time application support by using a memory system which manages computer intensive and time critical data and their complex transfers.

• Provides hardware reconfigurability by using application specific accelerators which allow sensor system architect to port more features in hardware without changing the system architecture.

• Consumes low power by utilizing a front-end interface that handles multiple sensors and their 1D/2D data transfers.

• Provides energy efficacy and high speed by using an on-chip scheduler which handles multiple sensors and processing cores.

• Offers programming toolkit which helps sensor application programmers to write their code easily and efficiently.

• When compared to a baseline sensor system, the ISSA improves the application performance up to 7.5 times, draws 15.6% less dynamic power and consumes 8.9 times less energy.